Maxim > Design Support > Technical Documents > Application Notes > Interface Circuits > APP 5306

Keywords: UART, RS232, RS485, SPI, I2C, half duplex, HDX, full duplex, FDX, WLP, wafer level package, FIFO, CTS, RTS, clear to send, ready to send, baud

# APPLICATION NOTE 5306 Programming Baud Rates of the MAX3108 UART

By: Micheal Scherrenburg Mar 30, 2012

Abstract: The MAX3108 is a complete high-performance universal asynchronous receiver-transmitter (UART) in a tiny 2.1mm × 2.1mm wafer level package (WLP). It provides many high-end features in hardware, thus reducing firmware complexity. Instead of fast response and intensive firmware management, most of the MAX3108's advanced features need only initial firmware setup and little or no firmware management. This application note, one in a series explaining the MAX3108 features in detail, explains how to set target baud rates.

#### Introduction

The MAX3108, a high-performance universal asynchronous receiver-transmitter (UART) in a wafer-level package (WLP), is packed with many advanced features in hardware, from individual 128 word transmit and receive FIFOs to extensive hardware-mediated flow control. Most of the MAX3108's functionality relies on the programming of a clock. So, one of the first programming tasks is to set an appropriate baud rate clock.

This application note explains how to program the five registers (and 1 bit) to set a desired baud rate. A spreadsheet is provided that greatly simplifies the task of UART baud rate programming. This document presumes that the reader is already familiar with the application note 5304, "Interfacing to the MAX3108 UART."

## **Baud Rate Generation**

This section describes how the MAX3108 creates a baud rate frequency from a crystal or oscillator input. This should be done first when programming the UART. Except for the SPI/I<sup>2</sup>C interface and basic GPIO functionality, nothing else in the MAX3108 functions until a clock rate is programmed. The device comes out of reset with clocks disabled if using a crystal as a frequency source.

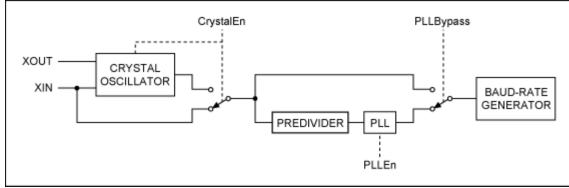

The MAX3108 processes a clock source into an output baud rate in the following way:

- If the clock source is a crystal, the crystal oscillator block converts this source to an internal logic level clock. The MAX3108 accepts crystals that resonate between 1MHz and 4MHz. To enable the crystal oscillator, set the CrystalEN bit to 1. Alternatively, an external logic level clock source may be provided at the XIN pin of the MAX3108. The MAX3108 accepts a clock frequency from 500kHz to 35MHz. Because the CrystalEn bit defaults to 0 at power-up or after reset, it will use an external clock unless specifically programmed otherwise.

- 2. The clock from step 1 feeds the input of a predivider. It divides the input frequency by a number between 1 and 63. Bits 5 through 0 of the PLLConfig register define the divisor.

- 3. The output of the predivider feeds a phase-locked loop (PLL), which multiplies the frequency of the predivider by

1, 6, 48, 96, or 144. To multiply by 1, set bit 2, the PLLEn bit of the CLKSource register, to 0. To set any other multiplier, set the PLLEn bit to 1, and also set bits 7 and 6 of the PLLConfig register as illustrated in Table 4 of the MAX3108 data sheet, which also details the frequency limits of the PLL. Note that the PLL cannot be used at all if the supply Voltage ( $V_{CC}$ ) is less than 2.35V. The PLL is useful when generating high baud rates from low frequency clock sources.

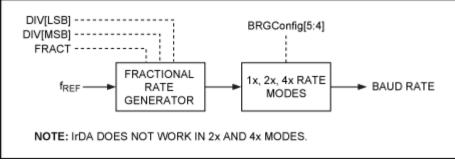

4. The output of the PLL feeds a baud rate generator, whose output frequency is divided. This circuit divides its input frequency by an integer part (from 1 through 65,535) and a fractional part (from 0/16 through 15/16). This is programmed through the DIVMSB register, the DIVLSB register, and bits 3 through 0 of the BRGConfig register. The output of the baud rate generator is the internal baud rate clock. The actual baud rate would be the frequency output of the baud rate generator divided by 16. One can divide by 8 or by 4 instead, but dividing by 16 should be used if at all possible. Dividing by 8 or by 4 makes some features unusable, and reduces the frequency error tolerance of the MAX3108 UART receiver.

Figure 1. The MAX3108 clock selection diagram.

Figure 2. 2x and 4x baud rates.

| Table 1. Differences between 1x, 2x, and 4x Rate Modes |              |   |                  |                               |                                      |

|--------------------------------------------------------|--------------|---|------------------|-------------------------------|--------------------------------------|

| Rate Mode<br>Divider                                   | BRGConfig[5] |   | IrDA<br>Capable? | Line Noise<br>Detect Capable? | Receive Frequency<br>Error Tolerance |

| 16                                                     | 0            | 0 | Yes              | Yes                           | Best                                 |

| 8                                                      | 0            | 1 | No               | Yes                           | Very good                            |

| 4                                                      | 1            | 0 | No               | No                            | Good                                 |

The crystal oscillator operates with common UART crystals, such as 1.8432MHz, and the external clock input works with a range of common clock frequencies found in embedded systems. This is a lot of information to digest just to

generate a baud rate clock. Also, for most baud rates, the same baud rate can be generated in many ways.

### **Baud Rate Assistance Spreadsheet**

For this reason, the "MAX3108 Freq Select" spreadsheet is available for download. Based on a given input frequency and desired baud rate, this tool makes it easy to determine what to program into the MAX3108's five clock configuration registers. The spreadsheet calculates a few of the best ways to generate the target baud rate from the given input frequency.

In many cases, the target baud rate can be generated exactly. Sometimes however, the best possible configuration results in a small error in the generated baud rate. This is why the spreadsheet provides more than one possible configuration. Each possibility yields the closest frequency match, but with different assumptions.

Most of the time, there will be one configuration that is obviously superior. After describing the spreadsheet, we will work through some examples to show how easy it is to determine the best correct configuration to program into the MAX3108.

### **Spreadsheet Description**

The spreadsheet needs only four inputs from the user, all near the top of the **Synthesize** tab.

|   | А    | В                     | С       | D |

|---|------|-----------------------|---------|---|

| 1 | 1.21 |                       |         |   |

| 2 |      | XIN Frequency:        | 1843200 |   |

| 3 |      | Desired BAUD Rate:    | 230400  |   |

| 4 |      |                       |         |   |

| 5 |      | Crystal (Y/N)?        | У       |   |

| 6 |      | CLK on RTS PIN (Y/N)? | n       |   |

| 7 |      |                       |         |   |

Enter the four parameters as follows:

- 1. In cell C2, enter the crystal frequency or the external oscillator frequency, in Hertz.

- 2. In cell C3, enter the desired baud rate, in bits per second.

- 3. In cell C5, enter **y** if the frequency source is a crystal (that uses the MAX3108 crystal oscillator), or enter **n** if the frequency source is an external clock supplied to the MAX3108 XIN pin.

- 4. In cell C6, enter n. This pertains to a MAX3108 feature that will be described later.

The results appear starting in row 8.

|    | А | В                   | С    |  |

|----|---|---------------------|------|--|

| 7  |   |                     |      |  |

| 8  |   | XIN Test (XTAL):    | TRUE |  |

| 9  |   | XIN Test (Ext OSC): | TRUE |  |

| 10 |   |                     |      |  |

| 11 |   | Can it be done?     | TRUE |  |

|    |   |                     |      |  |

If cell C8 reports **FALSE**, then you have chosen a crystal as the frequency source, and it is out of the range of valid frequencies for the MAX3108 crystal oscillator circuit. Valid crystal oscillator frequencies range between 1MHz and 4MHz.

If cell C9 reports **FALSE**, then you have chosen an external clock source, and the frequency you have specified is outside the range of valid clock frequencies for the XIN pin. Valid external oscillator frequencies range between 0.5MHz and 35MHz.

Cell C11 reports if it is at all possible to reasonably generate the desired baud rate. Cell C11 can report **FALSE** because cells C8 or C9 report **FALSE**. Or because no configuration exists that can reasonably achieve the target baud rate. For example, requesting a baud rate above the MAX3108's maximum of 24MBd causes cell C11 to report **FALSE** regardless of the values of the other user entries.

Further results appear starting in row 13.

Columns D, E, and F calculate the configuration with the lowest frequency error, each under a different assumption. Column D assumes that the rate mode is fixed at 16, column E assumes that the rate mode is fixed at 8, and column F assumes that the rate mode is fixed at 4. As a general rule, the rate mode should be kept at 16, unless there is a compelling reason to choose otherwise, a topic that we will return to soon.

Row 14 is a flag, which if **FALSE**, indicates that the corresponding rate mode cannot be used in any configuration that produces a result near the desired baud rate. In this case, the other entries in this column will be blank.

Rows 15 through 17 and row 20 describe the configuration in a way that can be understood via Figures 1 and 2. Row 15 describes the predivider value chosen. Row 20 indicates which PLL multiplier was chosen. Additionally, rows 16 and 17 describe the integer and fractional part of the fractional rate generator. Of more direct interest, row 17, shows the actual baud rate generated, and row 18, contains the frequency error, in percent.

Rows 21 through 25 represent the values to program into the five MAX3108 clock configuration registers, in hex. When a configuration is selected by the user, these five hex values are copied into a program, to be described later, to load these values into the MAX3108.

## A First Example

Let's begin with a simple example, generating 19.2kBd from a 1.8432MHz crystal. Enter the following parameters:

|   | А    | В                     | С       |

|---|------|-----------------------|---------|

| 1 | 1.21 |                       |         |

| 2 |      | XIN Frequency:        | 1843200 |

| 3 |      | Desired BAUD Rate:    | 19200   |

| 4 |      |                       |         |

| 5 |      | Crystal (Y/N)?        | У       |

| 6 |      | CLK on RTS PIN (Y/N)? | n       |

| - |      |                       |         |

This is the result:

|    | А | В                        | С | D       | E      | F      |  |

|----|---|--------------------------|---|---------|--------|--------|--|

| 13 |   | Best, for each Rate Mode |   | RM = 16 | RM = 8 | RM = 4 |  |

| 14 |   | Flag:                    |   | TRUE    | TRUE   | TRUE   |  |

| 15 |   | Best Pre-Div:            |   | 1       | 1      | 1      |  |

| 16 |   | Best BRG INT:            |   | 6       | 12     | 24     |  |

| 17 |   | Best BRG Frac:           |   | 0       | 0      | 0      |  |

| 18 |   | Best Output BAUD Rate:   |   | 19200   | 19200  | 19200  |  |

| 19 |   | Best Percent Error:      |   | 0       | 0      | 0      |  |

| 20 |   | Best PLL Multiplier:     |   | x1      | x1     | x1     |  |

| 21 |   | PLLConfig value:         |   | 0x01    | 0x01   | 0x01   |  |

| 22 |   | BRGConfig Value:         |   | 0x00    | 0x10   | 0x20   |  |

| 23 |   | DIVLSB Value:            |   | 0x06    | 0x0C   | 0x18   |  |

| 24 |   | DIVMSB Value:            |   | 0x00    | 0x00   | 0x00   |  |

| 25 |   | CLKSource Value:         |   | 0x0A    | 0x0A   | 0x0A   |  |

| 20 |   |                          |   |         |        |        |  |

Note that cell D19 indicates zero frequency error, at least with regards to the MAX3108 conversion process from frequency input to baud rate output. This is the best scenario, where rate mode is 16. Consult cells D21 through D25 to determine what to program into the MAX3108 clock configuration registers. You will find that, in the majority of the cases, you will select cells D21 though D25 to program the desired baud rate.

## An Example with a Frequency Error

Now let's try a different example. Let's generate 190kBd from a 1.8432MHz crystal. Enter the following parameters:

|   | А    | В                     | С       |

|---|------|-----------------------|---------|

| 1 | 1.21 |                       |         |

| 2 |      | XIN Frequency:        | 1843200 |

| 3 |      | Desired BAUD Rate:    | 190000  |

| 4 |      |                       |         |

| 5 |      | Crystal (Y/N)?        | у       |

| 6 |      | CLK on RTS PIN (Y/N)? | n       |

|   |      |                       |         |

Please note the different result:

|    | А | В                        | С | D           | E           | F           |  |

|----|---|--------------------------|---|-------------|-------------|-------------|--|

| 13 |   | Best, for each Rate Mode |   | RM = 16     | RM = 8      | RM = 4      |  |

| 14 |   | Flag:                    |   | TRUE        | TRUE        | TRUE        |  |

| 15 |   | Best Pre-Div:            |   | 4           | 3           | 4           |  |

| 16 |   | Best BRG INT:            |   | 21          | 38          | 87          |  |

| 17 |   | Best BRG Frac:           |   | 13          | 13          | 5           |  |

| 18 |   | Best Output BAUD Rate:   |   | 190129.5129 | 189959.4203 | 189993.4145 |  |

| 19 |   | Best Percent Error:      |   | 0.068164681 | 0.021357742 | 0.003466074 |  |

| 20 |   | Best PLL Multiplier:     |   | x144        | x96         | x144        |  |

| 21 |   | PLLConfig value:         |   | 0xC4        | 0x83        | 0xC4        |  |

| 22 |   | BRGConfig Value:         |   | 0x0D        | 0x1D        | 0x25        |  |

| 23 |   | DIVLSB Value:            |   | 0x15        | 0x26        | 0x57        |  |

| 24 |   | DIVMSB Value:            |   | 0x00        | 0x00        | 0x00        |  |

| 25 |   | CLKSource Value:         |   | 0x06        | 0x06        | 0x06        |  |

Now, we have a small error for a rate mode of 16, and less error for the other rate modes. In this case, the error is small enough that the cell D21 through D25 values should be used.

What is a small enough error? In general, a frequency error of 0.8% or less should be no cause for concern. However, a frequency error of 2.0% or higher should be looked at carefully. Errors between 0.8% and 2.0% involve some judgment. In this case, the frequency error with a rate mode of 16 is about 0.07%, more than small enough to make it the best choice for configuration.

# An Example with a Large Frequency Error

We will now try something that shows why we may need to sometimes choose columns E or F. To begin, let's generate 5.678901MBd from a 28.23MHz clock. Enter the following parameters:

|   | А | В                     | С       |  |

|---|---|-----------------------|---------|--|

| 2 |   | XIN Frequency:        | 1843200 |  |

| 3 |   | Desired BAUD Rate:    | 5678901 |  |

| 4 |   |                       |         |  |

| 5 |   | Crystal (Y/N)?        | n       |  |

| 6 |   | CLK on RTS PIN (Y/N)? | n       |  |

| 7 |   |                       |         |  |

Here, we obtain a more interesting result:

|    | А | В                        | С | D           | E           | F           |

|----|---|--------------------------|---|-------------|-------------|-------------|

| 13 |   | Best, for each Rate Mode |   | RM = 16     | RM = 8      | RM = 4      |

| 14 |   | Flag:                    |   | TRUE        | TRUE        | TRUE        |

| 15 |   | Best Pre-Div:            |   | 2           | 2           | 2           |

| 16 |   | Best BRG INT:            |   | 1           | 1           | 1           |

| 17 |   | Best BRG Frac:           |   | 0           | 15          | 15          |

| 18 |   | Best Output BAUD Rate:   |   | 5529600     | 5707974.194 | 5707974.194 |

| 19 |   | Best Percent Error:      |   | 2.629047416 | 0.511951054 | 0.511951054 |

| 20 |   | Best PLL Multiplier:     |   | x96         | x96         | x48         |

| 21 |   | PLLConfig value:         |   | 0x82        | 0x82        | 0x42        |

| 22 |   | BRGConfig Value:         |   | 0x00        | 0x1F        | 0x2F        |

| 23 |   | DIVLSB Value:            |   | 0x01        | 0x01        | 0x01        |

| 24 |   | DIVMSB Value:            |   | 0x00        | 0x00        | 0x00        |

| 25 |   | CLKSource Value:         |   | 0x04        | 0x04        | 0x04        |

Note the frequency error with a rate mode of 16 is 2.63%, which is too high. If the MAX3108 IRDA feature is used, the rate mode must be set to 16. In this case, perhaps a different input frequency can be chosen, 18MHz for example. Or perhaps a more careful analysis of channel timing can be undertaken, to verify if this error does not impact the specific system being designed.

Another alternative is to choose the configuration with the rate mode set at 8. This results in a very respectable 0.5% frequency error. In this situation, the parameters to program the MAX3108 clock configuration registers would be taken from cells E21 through E25.

## An Example with More Limited Choices

For output rates greater than 6MBd, the rate mode cannot be 16. This is another reason why one of the other rate modes must be selected. Even below 6MBd, some combinations of input frequencies and output baud rates conspire to disallow the case where rate mode is 16. As an example, try to generate 5.775MBd from a 1.8432MHz crystal.

|   | А    | В                     | С       |

|---|------|-----------------------|---------|

| 1 | 1.22 |                       |         |

| 2 |      | XIN Frequency:        | 1843200 |

| 3 |      | Desired BAUD Rate:    | 5775000 |

| 4 |      |                       |         |

| 5 |      | Crystal (Y/N)?        | У       |

| 6 |      | CLK on RTS PIN (Y/N)? | n       |

| _ |      |                       |         |

The result is:

|    | А | В                        | С | D       | E           | F           |  |

|----|---|--------------------------|---|---------|-------------|-------------|--|

| 13 |   | Best, for each Rate Mode |   | RM = 16 | RM = 8      | RM = 4      |  |

| 14 |   | Flag:                    |   | FALSE   | TRUE        | TRUE        |  |

| 15 |   | Best Pre-Div:            |   |         | 4           | 4           |  |

| 16 |   | Best BRG INT:            |   |         | 1           | 2           |  |

| 17 |   | Best BRG Frac:           |   |         | 7           | 14          |  |

| 18 |   | Best Output BAUD Rate:   |   |         | 5770017.391 | 5770017.391 |  |

| 19 |   | Best Percent Error:      |   |         | 0.086278938 | 0.086278938 |  |

| 20 |   | Best PLL Multiplier:     |   |         | x144        | x144        |  |

| 21 |   | PLLConfig value:         |   |         | 0xC4        | 0xC4        |  |

| 22 |   | BRGConfig Value:         |   |         | 0x17        | 0x2E        |  |

| 23 |   | DIVLSB Value:            |   |         | 0x01        | 0x02        |  |

| 24 |   | DIVMSB Value:            |   |         | 0x00        | 0x00        |  |

| 25 |   | CLKSource Value:         |   |         | 0x06        | 0x06        |  |

|    |   |                          |   |         |             |             |  |

In this case, a rate mode of 16 cannot be used at all. Either the input frequency must be changed, or a rate mode of 8 must be chosen. Note, in some cases, a rate mode of 8 is also not an option. For example, when the output baud rate is greater than 12MBd, the only possible rate mode is 4.

## **Programming the MAX3108**

Once a set of programming parameters has been chosen from the spreadsheet, programming the MAX3108 is a straightforward task. When loading all the registers at power-up, these five registers comprise part of the set being loaded. This section describes how to program the MAX3108 for a target baud rate, presuming there is not yet any serial data flow. Further steps must be taken when changing an existing baud rate. These steps will be explained in a future application note. Let's begin with an example where the frequency source is an external clock, say, generating 190kBd from a 28.23MHz external clock source on the MAX3108 XIN pin. The input section of the spreadsheet would look like:

|   | А    | В                     | С        |

|---|------|-----------------------|----------|

| 1 | 1.22 |                       |          |

| 2 |      | XIN Frequency:        | 28230000 |

| 3 |      | Desired BAUD Rate:    | 190000   |

| 4 |      |                       |          |

| 5 |      | Crystal (Y/N)?        | n        |

| 6 |      | CLK on RTS PIN (Y/N)? | n        |

The results are:

|    | А | В                        | С | D           | E           | F           |

|----|---|--------------------------|---|-------------|-------------|-------------|

| 13 |   | Best, for each Rate Mode |   | RM = 16     | RM = 8      | RM = 4      |

| 14 |   | Flag:                    |   | TRUE        | TRUE        | TRUE        |

| 15 |   | Best Pre-Div:            |   | 55          | 37          | 37          |

| 16 |   | Best BRG INT:            |   | 24          | 48          | 96          |

| 17 |   | Best BRG Frac:           |   | 5           | 3           | 6           |

| 18 |   | Best Output BAUD Rate:   |   | 190003.2718 | 190001.0516 | 190001.0516 |

| 19 |   | Best Percent Error:      |   | 0.001721996 | 0.000553492 | 0.000553492 |

| 20 |   | Best PLL Multiplier:     |   | x144        | x96         | x96         |

| 21 |   | PLLConfig value:         |   | 0xF7        | 0xA5        | 0xA5        |

| 22 |   | BRGConfig Value:         |   | 0x05        | 0x13        | 0x26        |

| 23 |   | DIVLSB Value:            |   | 0x18        | 0x30        | 0x60        |

| 24 |   | DIVMSB Value:            |   | 0x00        | 0x00        | 0x00        |

| 25 |   | CLKSource Value:         |   | 0x04        | 0x04        | 0x04        |

Here is the program to load the MAX3108 clock configuration registers to generate the target baud rate. Note that the parameters filled into array U190K in the program are copied from cells D21 through D25 in the spreadsheet.

```

/*

** Run UART at 190KBAUD from a 28.23MHz clock source

*/

unsigned char U190K [] = {

0xF7, 0x05, 0x18, 0x00, 0x04

};

// Load the MAX3108 clock configuration registers appropriately

//

if (!MAX3108_Puts (MAX3108R_PLLCONFIG, sizeof U190K, U190K)) {

// handle possible I<sup>2</sup>C protocol error here

}

```

### **A Second Programming Example**

For another example, let's generate 230.4kBd from a 1.8432MHz crystal as input. This is a very common crystal for UART clock generation. The input section of the spreadsheet would look like:

|   | А    | В                     | С       |

|---|------|-----------------------|---------|

| 1 | 1.22 |                       |         |

| 2 |      | XIN Frequency:        | 1843200 |

| 3 |      | Desired BAUD Rate:    | 230400  |

| 4 |      |                       |         |

| 5 |      | Crystal (Y/N)?        | у       |

| 6 |      | CLK on RTS PIN (Y/N)? | n       |

| 7 |      |                       |         |

The results are:

|    | А | В                        | С | D       | E      | F      |

|----|---|--------------------------|---|---------|--------|--------|

| 13 |   | Best, for each Rate Mode |   | RM = 16 | RM = 8 | RM = 4 |

| 14 |   | Flag:                    |   | TRUE    | TRUE   | TRUE   |

| 15 |   | Best Pre-Div:            |   | 3       | 1      | 1      |

| 16 |   | Best BRG INT:            |   | 1       | 1      | 2      |

| 17 |   | Best BRG Frac:           |   | 0       | 0      | 0      |

| 18 |   | Best Output BAUD Rate:   |   | 230400  | 230400 | 230400 |

| 19 |   | Best Percent Error:      |   | 0       | 0      | 0      |

| 20 |   | Best PLL Multiplier:     |   | хб      | x1     | x1     |

| 21 |   | PLLConfig value:         |   | 0x03    | 0x01   | 0x01   |

| 22 |   | BRGConfig Value:         |   | 0x00    | 0x10   | 0x20   |

| 23 |   | DIVLSB Value:            |   | 0x01    | 0x01   | 0x02   |

| 24 |   | DIVMSB Value:            |   | 0x00    | 0x00   | 0x00   |

| 25 |   | CLKSource Value:         |   | 0x06    | 0x0A   | 0x0A   |

When the clock source is a crystal, you have the option of verifying crystal operation. The ClkReady bit in the STSInt register asserts only when the crystal oscillator and the PLL are operating and locked. For a given MAX3108 clock configuration that is known to be working, this reduces to verification that the crystal oscillator is running as expected. The ClkReady bit **does not work** if using an external clock source, so do not test it if an external clock feeds the MAX3108.

Though useful in a development environment, this feature is probably of little use in production or in equipment deployed in the field. Note that other bits in the STSInt register are cleared upon read. There is no way to check the ClkReady bit without also clearing a possible TxEmptyInt or GPIxInt condition. Programmers beware!

In the case of an external clock, if the predivider or PLL factor is changed, the UART will not be ready to transmit or receive immediately. After changing the predivider or PLL factor, or after enabling the PLL, the UART will function at the new programmed baud rate after a time delay of 1200 × (predivider)/(XIN frequency) or less.

```

/*

** Run UART at 230.4KBAUD from a 1.8432MHz crystal

*/

unsigned char U230K4 [] = {

0x03, 0x00, 0x01, 0x00, 0x06

};

// Load the MAX3108 clock configuration registers appropriately

//

if (!MAX3108_Puts (MAX3108R_PLLCONFIG, sizeof U230K4, U230K4)) {

// handle possible I<sup>2</sup>C protocol error here

}

// Check XTAL and PLL are running OK - optional

while (MAX3108_Read (MAX3108R_STSINT & 0x0008) == 0) ;

```

# **Avoiding PLL Changes**

So far, we have been using the results from rows 13 through 25. Another section (in rows 27 through 39) has slightly different assumptions. In this second section, configurations with the lowest frequency error are calculated, but with the PLL fixed at different rates.

This comes in handy when generating multiple baud rates from a single frequency source, without incurring the delay associated with PLL relock. This means that the predivider and PLL must not change between the various configurations.

One example of this would be in an IO-Link® scenario, where it is important to be able to change quickly between 230.4kBd 38.4kBd, and 4.8kBd. Let's see how this can be accomplished, assuming our ubiquitous 1.8432MHz crystal. Starting with the highest baud rate, the input section of the spreadsheet would look like:

|   | А    | В                     | С       |

|---|------|-----------------------|---------|

| 1 | 1.22 |                       |         |

| 2 |      | XIN Frequency:        | 1843200 |

| 3 |      | Desired BAUD Rate:    | 4800    |

| 4 |      |                       |         |

| 5 |      | Crystal (Y/N)?        | У       |

| 6 |      | CLK on RTS PIN (Y/N)? | n       |

| _ |      |                       |         |

This results in:

|    | А | В                        | С | D       | E      | F      |

|----|---|--------------------------|---|---------|--------|--------|

| 13 |   | Best, for each Rate Mode |   | RM = 16 | RM = 8 | RM = 4 |

| 14 |   | Flag:                    |   | TRUE    | TRUE   | TRUE   |

| 15 |   | Best Pre-Div:            |   | 3       | 1      | 1      |

| 16 |   | Best BRG INT:            |   | 1       | 1      | 2      |

| 17 |   | Best BRG Frac:           |   | 0       | 0      | 0      |

| 18 |   | Best Output BAUD Rate:   |   | 230400  | 230400 | 230400 |

| 19 |   | Best Percent Error:      |   | 0       | 0      | 0      |

| 20 |   | Best PLL Multiplier:     |   | хб      | x1     | x1     |

| 21 |   | PLLConfig value:         |   | 0x03    | 0x01   | 0x01   |

| 22 |   | BRGConfig Value:         |   | 0x00    | 0x10   | 0x20   |

| 23 |   | DIVLSB Value:            |   | 0x01    | 0x01   | 0x02   |

| 24 |   | DIVMSB Value:            |   | 0x00    | 0x00   | 0x00   |

| 25 |   | CLKSource Value:         |   | 0x06    | 0x0A   | 0x0A   |

Let's start with the assumption that rate mode can be 16. Note the predivider and the PLL factor, 3 and x6, respectively. If this works, we would use the configuration values in cells D21 through D25 to program the MAX3108 for 230.4kBd. Now, let's try the next baud rate.

|   | А    | В                     | С       |

|---|------|-----------------------|---------|

| 1 | 1.22 |                       |         |

| 2 |      | XIN Frequency:        | 1843200 |

| 3 |      | Desired BAUD Rate:    | 38400   |

| 4 |      |                       |         |

| 5 |      | Crystal (Y/N)?        | у       |

| 6 |      | CLK on RTS PIN (Y/N)? | n       |

| 7 |      |                       |         |

The result in this case is:

|    | А | В                        | С | D       | E      | F      |

|----|---|--------------------------|---|---------|--------|--------|

| 13 |   | Best, for each Rate Mode |   | RM = 16 | RM = 8 | RM = 4 |

| 14 |   | Flag:                    |   | TRUE    | TRUE   | TRUE   |

| 15 |   | Best Pre-Div:            |   | 1       | 1      | 1      |

| 16 |   | Best BRG INT:            |   | 3       | 6      | 12     |

| 17 |   | Best BRG Frac:           |   | 0       | 0      | 0      |

| 18 |   | Best Output BAUD Rate:   |   | 38400   | 38400  | 38400  |

| 19 |   | Best Percent Error:      |   | 0       | 0      | 0      |

| 20 |   | Best PLL Multiplier:     |   | x1      | x1     | x1     |

| 21 |   | PLLConfig value:         |   | 0x01    | 0x01   | 0x01   |

| 22 |   | BRGConfig Value:         |   | 0x00    | 0x10   | 0x20   |

| 23 |   | DIVLSB Value:            |   | 0x03    | 0x06   | 0x0C   |

| 24 |   | DIVMSB Value:            |   | 0x00    | 0x00   | 0x00   |

| 25 |   | CLKSource Value:         |   | 0x0A    | A0x0   | 0x0A   |

None of these entries has a PLL factor of x6, so let's now consult the second section.

|    | Α | В                       | С | D       | E       | F       | G       | н       |

|----|---|-------------------------|---|---------|---------|---------|---------|---------|

| 27 |   | Best, for each PLL Mult |   | x1      | хб      | x48     | x96     | x144    |

| 28 |   | Flag:                   |   | TRUE    | TRUE    | TRUE    | TRUE    | TRUE    |

| 29 |   | Best Pre-Div:           |   | 1       | 3       | 2       | 2       | 3       |

| 30 |   | Best BRG INT:           |   | 3       | 6       | 72      | 144     | 144     |

| 31 |   | Best BRG Frac:          |   | 0       | 0       | 0       | 0       | 0       |

| 32 |   | Best Output BAUD Rate:  |   | 38400   | 38400   | 38400   | 38400   | 38400   |

| 33 |   | Best Percent Error:     |   | 0       | 0       | 0       | 0       | 0       |

| 34 |   |                         |   | RM = 16 |

| 35 |   | PLLConfig value:        |   | 0x01    | 0x03    | 0x42    | 0x82    | 0xC3    |

| 36 |   | BRGConfig Value:        |   | 0x00    | 0x00    | 0x00    | 0x00    | 0x00    |

| 37 |   | DIVLSB Value:           |   | 0x03    | 0x06    | 0x48    | 0x90    | 0x90    |

| 38 |   | DIVMSB Value:           |   | 0x00    | 0x00    | 0x00    | 0x00    | 0x00    |

| 39 |   | CLKSource Value:        |   | 0x0A    | 0x06    | 0x06    | 0x06    | 0x06    |

Column E provides configuration under the assumption that the PLL factor must be x6. Note that the predivider value is also 3. This means that the PLL will not need to relock going from 230.4kBd to 38.4kBd, if we choose to configure

the 38.4kBd output rate with the parameters given in cells E35 through E39.

We need to check that we can do this with 4.8kBd as well. The input section of the spreadsheet would look like:

|   | А    | В                     | С       |

|---|------|-----------------------|---------|

| 1 | 1.22 |                       |         |

| 2 |      | XIN Frequency:        | 1843200 |

| 3 |      | Desired BAUD Rate:    | 4800    |

| 4 |      |                       |         |

| 5 |      | Crystal (Y/N)?        | У       |

| 6 |      | CLK on RTS PIN (Y/N)? | n       |

| _ |      |                       |         |

The result is:

|    | А | В                        | С | D         | E         | F      |

|----|---|--------------------------|---|-----------|-----------|--------|

| 13 |   | Best, for each Rate Mode |   | RM = 16   | RM = 8    | RM = 4 |

| 14 |   | Flag:                    |   | TRUE      | TRUE      | TRUE   |

| 15 |   | Best Pre-Div:            |   | 1         | 1         | 1      |

| 16 |   | Best BRG INT:            |   | 24        | 48        | 96     |

| 17 |   | Best BRG Frac:           |   | 0         | 0         | 0      |

| 18 |   | Best Output BAUD Rate:   |   | 4800      | 4800      | 4800   |

| 19 |   | Best Percent Error:      |   | 0         | 0         | 0      |

| 20 |   | Best PLL Multiplier:     |   | <b>x1</b> | <b>x1</b> | x1     |

| 21 |   | PLLConfig value:         |   | 0x01      | 0x01      | 0x01   |

| 22 |   | BRGConfig Value:         |   | 0x00      | 0x10      | 0x20   |

| 23 |   | DIVLSB Value:            |   | 0x18      | 0x30      | 0x60   |

| 24 |   | DIVMSB Value:            |   | 0x00      | 0x00      | 0x00   |

| 25 |   | CLKSource Value:         |   | 0x0A      | A0x0      | 0x0A   |

| 26 |   |                          |   |           |           |        |

Just like in the case of 38.4kBd, none of the results have a PLL factor of x6, so we consult the second section:

|    | Α | В                       | С | D       | E       | F       | G       | Н       |

|----|---|-------------------------|---|---------|---------|---------|---------|---------|

| 27 |   | Best, for each PLL Mult |   | x1      | хб      | x48     | x96     | x144    |

| 28 |   | Flag:                   |   | TRUE    | TRUE    | TRUE    | TRUE    | TRUE    |

| 29 |   | Best Pre-Div:           |   | 1       | 3       | 2       | 2       | 3       |

| 30 |   | Best BRG INT:           |   | 24      | 48      | 576     | 1152    | 1152    |

| 31 |   | Best BRG Frac:          |   | 0       | 0       | 0       | 0       | 0       |

| 32 |   | Best Output BAUD Rate:  |   | 4800    | 4800    | 4800    | 4800    | 4800    |

| 33 |   | Best Percent Error:     |   | 0       | 0       | 0       | 0       | 0       |

| 34 |   |                         |   | RM = 16 |

| 35 |   | PLLConfig value:        |   | 0x01    | 0x03    | 0x42    | 0x82    | 0xC3    |

| 36 |   | BRGConfig Value:        |   | 0x00    | 0x00    | 0x00    | 0x00    | 0x00    |

| 37 |   | DIVLSB Value:           |   | 0x18    | 0x30    | 0x40    | 0x80    | 0x80    |

| 38 |   | DIVMSB Value:           |   | 0x00    | 0x00    | 0x02    | 0x04    | 0x04    |

| 39 |   | CLKSource Value:        |   | 0x0A    | 0x06    | 0x06    | 0x06    | 0x06    |

And just like in the case of 38.4kBd, the x6 section shows we can generate 4.8kBd with a PLL factor of x6 and a predivider of 3, using the configuration parameters found in cells E35 through E39.

## Avoiding the PLL Altogether

It is best to avoid the PLL altogether in some scenarios. For example, the PLL does not function if the V<sub>CC</sub> supplied to the MAX3108 is below 2.35V. Also, if it is important to operate quickly after coming out of a low power mode, the PLL should be avoided. Suppose we need to generate 230.4kBd, 38.4kBd, and 4.8kBd from a 1.8432MHz crystal, but we also need to avoid using the PLL.

The easiest way to accomplish this would be to consult the section with the PLL factor fixed at x1 for all three instances of the spreadsheet. For a target baud rate of 230.4kBd, the second section is:

|    | Α | В                       | С | D      | E       | F       | G       | Н       |

|----|---|-------------------------|---|--------|---------|---------|---------|---------|

| 27 |   | Best, for each PLL Mult |   | x1     | хб      | x48     | x96     | x144    |

| 28 |   | Flag:                   |   | TRUE   | TRUE    | TRUE    | TRUE    | TRUE    |

| 29 |   | Best Pre-Div:           |   | 1      | 3       | 2       | 2       | 3       |

| 30 |   | Best BRG INT:           |   | 1      | 1       | 12      | 24      | 24      |

| 31 |   | Best BRG Frac:          |   | 0      | 0       | 0       | 0       | 0       |

| 32 |   | Best Output BAUD Rate:  |   | 230400 | 230400  | 230400  | 230400  | 230400  |

| 33 |   | Best Percent Error:     |   | 0      | 0       | 0       | 0       | 0       |

| 34 |   |                         |   | RM = 8 | RM = 16 | RM = 16 | RM = 16 | RM = 16 |

| 35 |   | PLLConfig value:        |   | 0x01   | 0x03    | 0x42    | 0x82    | 0xC3    |

| 36 |   | BRGConfig Value:        |   | 0x10   | 0x00    | 0x00    | 0x00    | 0x00    |

| 37 |   | DIVLSB Value:           |   | 0x01   | 0x01    | 0x0C    | 0x18    | 0x18    |

| 38 |   | DIVMSB Value:           |   | 0x00   | 0x00    | 0x00    | 0x00    | 0x00    |

| 39 |   | CLKSource Value:        |   | 0x0A   | 0x06    | 0x06    | 0x06    | 0x06    |

|    |   |                         |   |        |         |         |         |         |

Cells D35 through D39 report the required configuration for all three instances of the spreadsheet, one instance for each of the three desired baud rates. Since the PLL is not used in any of these three configurations, and since the predivider value does not change, switching between all three baud rates avoids delays from PLL relock.

## Keeping the Rate Mode High

If it is desired to keep the rate mode set at 16 and also avoid the PLL, the third results section, rows 41 through 53, should be consulted. Note that this is a fairly restrictive scenario, so this third section will often be blank to indicate that no such configuration can be reasonably achieved. As an example, let's generate a 190kBd output rate from a 28.32MHz external clock source.

The input section of the spreadsheet is:

|   | А    | В                     | С        |

|---|------|-----------------------|----------|

| 1 | 1.22 |                       |          |

| 2 |      | XIN Frequency:        | 28230000 |

| 3 |      | Desired BAUD Rate:    | 190000   |

| 4 |      |                       |          |

| 5 |      | Crystal (Y/N)?        | n        |

| 6 |      | CLK on RTS PIN (Y/N)? | n        |

The result in this case is:

|    | А | В                        | С | D           | E           | F           |  |

|----|---|--------------------------|---|-------------|-------------|-------------|--|

| 13 |   | Best, for each Rate Mode |   | RM = 16     | RM = 8      | RM = 4      |  |

| 14 |   | Flag:                    |   | TRUE        | TRUE        | TRUE        |  |

| 15 |   | Best Pre-Div:            |   | 55          | 37          | 37          |  |

| 16 |   | Best BRG INT:            |   | 24          | 48          | 96          |  |

| 17 |   | Best BRG Frac:           |   | 5           | 3           | 6           |  |

| 18 |   | Best Output BAUD Rate:   |   | 190003.2718 | 190001.0516 | 190001.0516 |  |

| 19 |   | Best Percent Error:      |   | 0.001721996 | 0.000553492 | 0.000553492 |  |

| 20 |   | Best PLL Multiplier:     |   | x144        | x96         | x96         |  |

| 21 |   | PLLConfig value:         |   | 0xF7        | 0xA5        | 0xA5        |  |

| 22 |   | BRGConfig Value:         |   | 0x05        | 0x13        | 0x26        |  |

| 23 |   | DIVLSB Value:            |   | 0x18        | 0x30        | 0x60        |  |

| 24 |   | DIVMSB Value:            |   | 0x00        | 0x00        | 0x00        |  |

| 25 |   | CLKSource Value:         |   | 0x04        | 0x04        | 0x04        |  |

For a rate mode of 16, the suggested configuration uses a PLL factor of x144, but we need a PLL factor of x1. This does not meet our requirement of a rate mode of 16 and a PLL factor of x1. Consulting the second results section:

| Α | В                       | С                                                                                                                                                                                                                                        | D                                                                                                                                                                                                                                                                 | E                                                                                                                                                                                                                  | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Best, for each PLL Mult |                                                                                                                                                                                                                                          | <b>x1</b>                                                                                                                                                                                                                                                         | хб                                                                                                                                                                                                                 | x48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | x96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | x144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | Flag:                   |                                                                                                                                                                                                                                          | TRUE                                                                                                                                                                                                                                                              | TRUE                                                                                                                                                                                                               | TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | Best Pre-Div:           |                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                 | 41                                                                                                                                                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | Best BRG INT:           |                                                                                                                                                                                                                                          | 18                                                                                                                                                                                                                                                                | 5                                                                                                                                                                                                                  | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | Best BRG Frac:          |                                                                                                                                                                                                                                          | 9                                                                                                                                                                                                                                                                 | 7                                                                                                                                                                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | Best Output BAUD Rate:  |                                                                                                                                                                                                                                          | 190101.0101                                                                                                                                                                                                                                                       | 189941.127                                                                                                                                                                                                         | 190014.3734                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 190001.0516                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 190003.272                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | Best Percent Error:     |                                                                                                                                                                                                                                          | 0.053163211                                                                                                                                                                                                                                                       | 0.030985791                                                                                                                                                                                                        | 0.007564925                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.000553492                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.001722                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                         |                                                                                                                                                                                                                                          | RM = 8                                                                                                                                                                                                                                                            | RM = 4                                                                                                                                                                                                             | RM = 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RM = 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RM = 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | PLLConfig value:        |                                                                                                                                                                                                                                          | 0x01                                                                                                                                                                                                                                                              | 0x29                                                                                                                                                                                                               | 0x59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0xA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0xEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |